Know Your Enemy, Know Yourself, Supplement: Pallas Programming Model

Learn about Pallas programming model that enables writing custom kernels on TPU.

Learn about Pallas programming model that enables writing custom kernels on TPU.

We explore the technical principles behind NVIDIA’s ICMS — a new storage tier designed to solve the KV cache capacity bottleneck in LLMs — and the Bluefield-4 DPU that manages it.

We explore the background of Groq and LPU, their hardware/software design philosophy, and analyze NVIDIA’s intentions behind acquiring Groq.

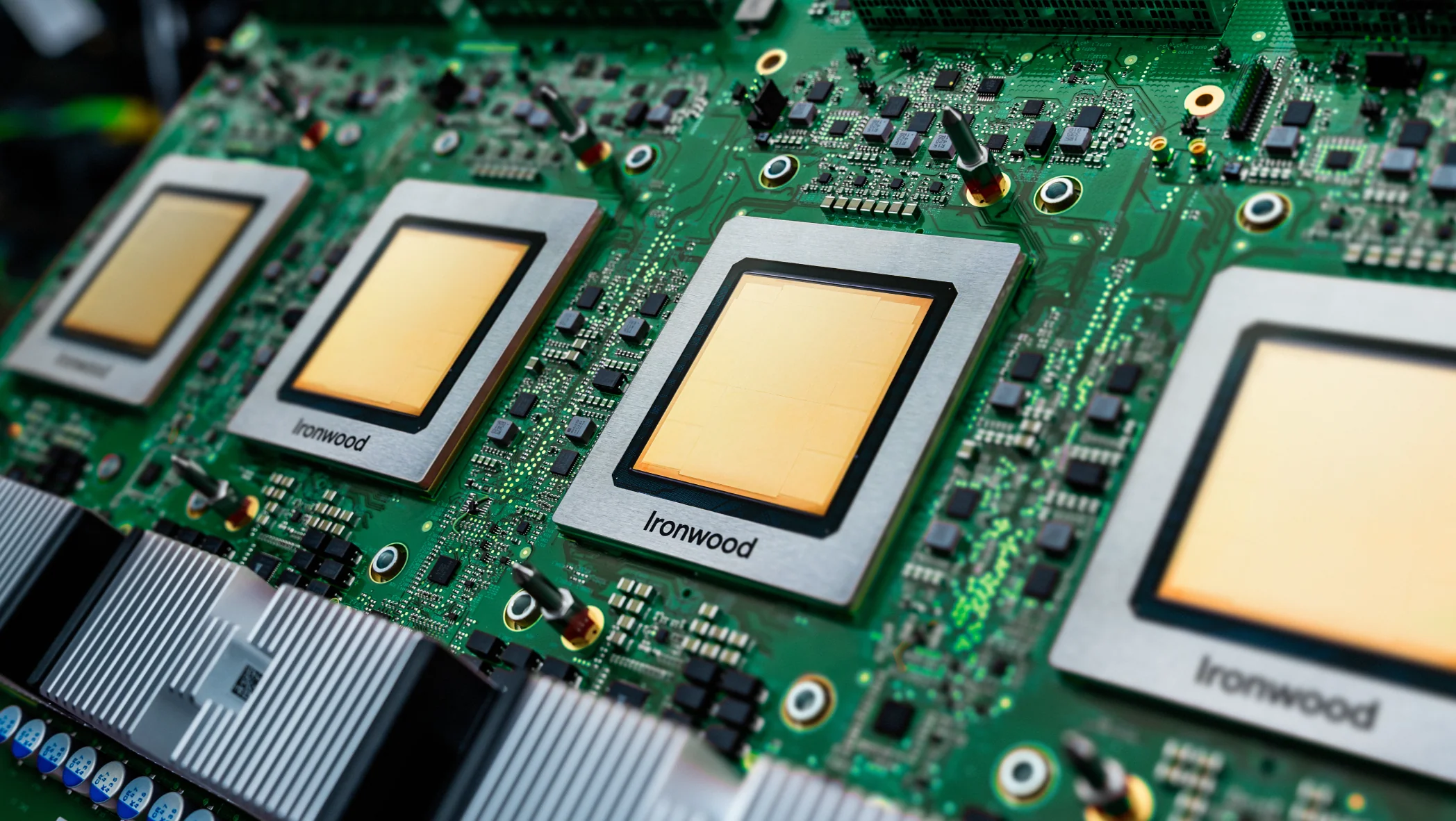

We explore the background of TPU’s emergence and analyze Google’s AI semiconductor strategy by examining its hardware and software architecture.